# DEPARTMENT OF SCIENTIFIC AND INDUSTRIAL RESEARCH NATIONAL PHYSICAL LABORATORY

## Progress Report

on the

Automatic Computing Engine

CONFIDENTIAL.

MA/17/1024.

DEPARTMENT OF SCIENTIFIC & INDUSTRIAL RESEARCH.

NATIONAL PHYSICAL LABORATORY.

PROGRESS REPORT ON THE AUTOMATIC COMPUTING ENGINE.

MATHEMATICS DIVISION. April, 1948.

PROGRESS REPORT ON THE AUTOMATIC COMPUTING ENGINE

- By -

J. H. WILKINSON.

SUMMARY.

This report gives a general introduction to the work carried out by Dr. Turing and his collaborators during the last two years at the National Physical Laboratory.

The report covers the general principles of both the design of the machine and the method of programming adopted for it. It includes a number of schematic diagrams of the circuits needed for the logical control and the arithmetic units. The circuits are given in some detail for a small pilot model containing some dozen delay lines and using a very simple logical control, and an indication of the extensions necessary for the full scale machine of some two hundred long delay lines is sketched. The programming of a number of problems is given, beginning with one or two simple examples which are complete in themselves, and proceeding to the development of routines which are of general application as components of large scale computing problems. As an example of a problem which requires the use of a number of standard routines, solution of a set of simultaneous linear algebraic equations by two different methods is given.

## 1. Introduction.

The A.C.E. belongs to the class of calculating machines usually known as "digital" machines. This class of machine consists of those which operate upon numbers directly in their digital form, as distinct from those which operate on physical quantities of which the numbers are the measures; the latter machines are usually called "analogue" machines. The fundamental advantage which digital machines possess over analogue machines, is their extreme flexibility. Typical digital machines are the ordinary desk calculating machines such as the Brunsviga, Friden and Marchant, and any of these may, in theory, be used for any problem which can be reduced to numerical computation. The limiting factor, in practice, is the time taken to perform the computation. This limiting factor makes itself felt, even in problems which, at first sight, may appear to be very simple. Consider, for example, the problem of solving a set of linear algebraic simultaneous equations by direct methods of computation. A typical method of solution is by the successive elimination of the variables, often known as pivotal condensation. For a set of equations of order n, the number of multiplications required for the solution is of the order n3/3; for a set of order 32 this already amounts to several weeks work, while a set of order 100 would probably take more than a year. It is the attempt to remove this restrictive time factor which has lead to the consideration of electronic computing machines.

In almost all calculating machines which have been constructed up to the present time, numbers have been represented in the conventional decimal scale. In the A.C.E., however, we intend to represent all numbers in the binary system. The explanation of this break with tradition is that it results in an enormous simplification in the equipment necessary for carrying out arithmetic operations. Every number may be represented in the binary system by a sequence of digits each of which is either a zero or a one, and this provides us with a particularly simple method of

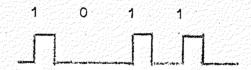

representing a number electrically. If we consider a sequence of electrical pulses at a fixed time interval apart, then to represent any number we may take a pulse pattern in which, corresponding to each one in the binary representation of the number, there is a pulse, and, corresponding to each zero, there is the absence of a pulse. Thus the number eleven, which is equivalent to 1011 in the binary system may be represented by the pulse pattern below

The number of digits necessary to represent a number in the binary scale is, of course, more than that necessary to represent that number in the decimal scale by a factor <a href="log210">log210</a>; thus to represent all ten digit decimal numbers a minimum of thirty-four binary digits is required. The simplicity of the arithmetic operations in the binary scale will be readily appreciated; in the process of multiplication for example, we have only to consider the two simple cases of multiplication by unity and by zero. In the A.C.E. the time between successive pulses will be 1 microsecond so that it will take only 34 microsecs, for a number of ten decimal digits to pass any given point on a conducting line. The fact that the successive digits of a number appear as a temporal sequence of pulses, characterises the machine as a "serial" operating machine. This is in contrast to a machine in which all the digits of a number are available simultaneously; such machines are known as "parallel" operation machines.

The employment of electronic equipment reduces the times needed for the fundamental operations of arithmetic by an enormous factor. Addition of two 32 digits binary numbers, for example, can be performed in 32 microsecs. on a serial machine with a pulse interval of 1 microsec, and the time of multiplication of two such numbers can be reduced to 64 microsecs. This enormous increase in speed necessitates an entirely different method of control

in an electronic computer. It would clearly be absurd, for example, to use the machine to perform a multiplication in the same way as is done on a desk calculating machine, since the time of reading the multiplier and multiplicand, communicating these values to the machine and writing down the answer would completely swamp the time taken for the actual multiplication.

If we return to the problem of the solution of a set of equations of order n, it will be seen that although approximately  $n^3/3$  intermediate numbers are obtained in the course of the computation, only the 'n' numbers, corresponding to the solution of the set, are of interest to the computer. In a high speed computer there must be some means of storing such intermediate numbers obtained during a computation, in a form in which they are available at a speed comparable with that at which the machine performs the arithmetic operations. The possession of a high speed "memory" of considerable capacity is thus seen to be a basic requirement of any efficient electronic computer. In the A.C.E. the high speed memory will consist of a number of elements known as accustic delay lines with a total storage capacity equivalent to approximately 6,000 twelve digit decimal numbers.

There is a further requirement before the machine can take full advantage of its speed. It must be possible to supply the instructions which the machine is to carry out at the same high speed. This may be achieved by representing these instructions in a coded numerical form and storing them in the memory in the same way as the numbers themselves; the machine must therefore possess a "logical control" which is capable of interpreting the coded instructions and causing them to be obeyed.

There is one final requirement which the electronic computer must meet. There must be some means of communicating with the outside world, both for the purpose of receiving initial data and instructions, and for communicating results. In its earliest version at least, the A.C.E. will use Hollerith punched card equipment to perform these input and output

functions. It will clearly be essential that it should be possible for the machine to accept data in decimal form and to provide solutions in the same form if needed, since the conversion from one system to the other is quite a lengthy process. Hence two most important instruction tables which the machine must be capable of interpreting are tables for decimal-binary and binary decimal conversion.

It might be imagined that a problem such as the solution of a set of linear equation of order 32 which required 10,000 multiplications would need so many instructions that the whole of the storage capacity would be completely filled with instructions. Fortunately this is not true because most computational problems can be reduced to a small number of cycles of operations each of which is repeated a great number of times. The machine must, however, have some means of discriminating whether one of these cycles has been repeated the requisite number of times, and as a result of this discrimination move to the next cycle of operations or repeat the current cycle.

The means by which the A.C.E. fulfils all the above requirements are the subject of the following paragraphs.

The account may be divided into two main sections. The first section deals with the design of the A.C.E. and the development of the appropriate code. It is not considered expedient at this stage to decide upon the details of the A.C.E. since many points will only be definitely determined in the light of engineering and coding experience gained from constructing and computing with a small pilot model. For this reason the details of the design and the code of such a pilot model are given first, and then a sketch only of the extensions envisaged in the full scale machine is given. This sketch is merely intended to be sufficient to form a background for the description of the type of code which the full scale A.C.E. will employ. The second section deals with the problem of programming, that is, of

preparing problems for computation on the machine. Although the detailed coding of problems has been given in terms of the code which has been adopted for the A.C.E., many of the considerations of this section are independent of any specific code. Before a large-scale problem can be coded for solution on an automatic computer a considerable amount of preliminary work is necessary even if the problem is already expressed in mathematical form, i.e. if the problem of translating a physical problem into a mathematical problem is excluded. The computational process appropriate to the mathematical problem has first to be decided upon and if this involves approximations, such as replacing derivatives by finite difference expressions, the limits of the error thereby introduced must be investigated. When a process which is satisfactory in this respect has been determined, an investigation into its stability with respect to the "rounding off" errors, which are inherent in digital computations, must be undertaken. Further, it is necessary that all the numbers derived during the course of the computation should be provided with scale factors which ensure that they do not grow out of the range permitted by the storage space allotted to them. This problem is somewhat more serious in automatic computation than in ordinary desk computation, because in the latter appropriate scale factors may be introduced by the operator as they become necessary and it is not important to anticipate when the necessity will arise. When all these points have been cleared up it is convenient to map out a general scheme of the method of computation and it is only after the completion of this scheme that the detailed coding begins. If the coding of each problem were attempted 'ab initio', the time taken to prepare a problem for computation might seriously reduce the effective speed of the machine. For this reason a considerable part of the section on programming is devoted to the problem of constructing tables of some generality for the standard routines which occur as elements of large scale problems. Generality is achieved by providing these standard routines with a number of parameters each

of which will be assigned a specific value, appropriate to the problem in hand, when the routine is used. In this way it is possible to prepare the greater part of any large scale computing problem for the machine by building it up from prefabricated units. Since these units are to be of very wide application, far more time and thought may be given to their preparation than would otherwise be justifiable. For this reason we have made a general principle of carrying out, concurrently with the mathematical investigation and the coding of a routine, a practical investigation on desk calculating machines. This is not because we regard the ordinary weapons of mathematical analysis as in any way inadequate for the task, but because the practical method often brings to light special points which are easily overlooked in a strictly theoretical approach. It should be emphasised that none of the instruction tables given in the second section are regarded in any respect as representing finished products. It is very unlikely that any of them will remain unaltered in the light of experience gained in using the machine. In spite of this we regard the preparation of these tables as being of real value since we believe that the successful use of electronic computing equipment will depend more upon the development of an efficient method of organising routines and their integration into large scale computing problems than upon any other single factor.

## 2. Symbols used in schematic circuits.

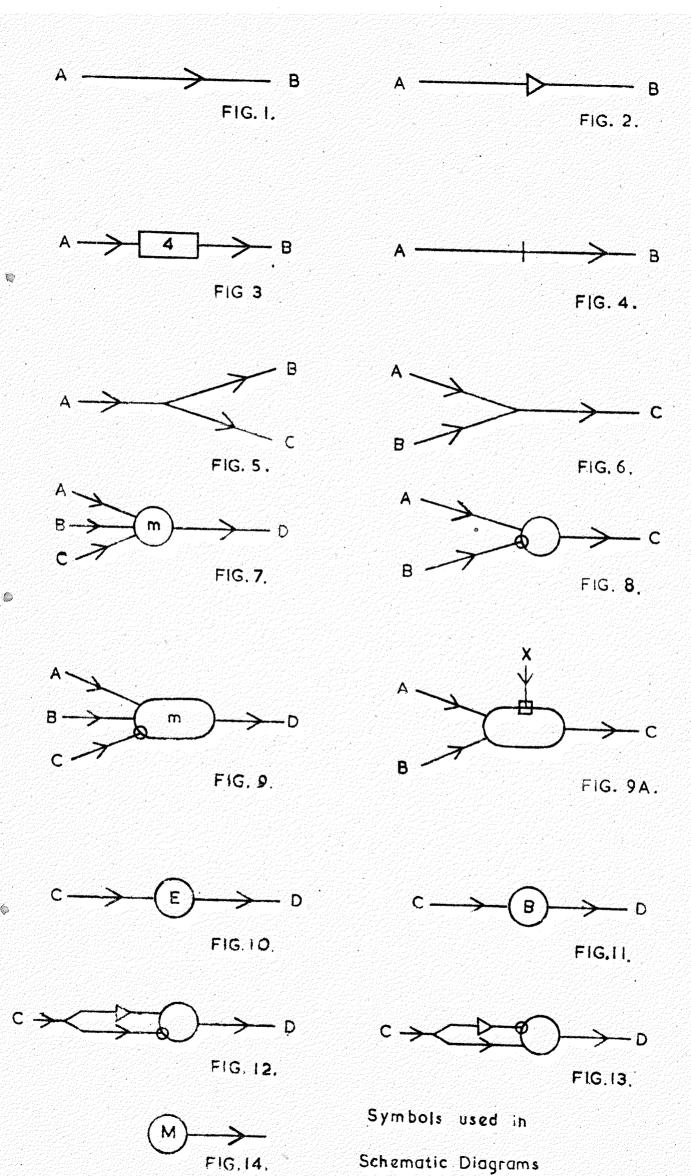

A number of special symbols are used in our schematic circuit diagrams, and for convenience these are collected and described below.

In the schematic circuits we consider the transmitted signals to be sequences of digits, each of which is a zero or a one. The actual electrical signal corresponding to a 'zero' or a 'one' will be different in different parts of a circuit. For instance, in a number of parts of the circuit, an unbroken sequence of ones may in fact be a D.C. voltage and an unbroken sequence of zeros, a different D.C. voltage. In the case where a one is a pulse, the centre of the pulse may occur at different times in different parts

of the circuit and the width and shape of the pulse may also vary. A full consideration of such points would be out of place in a report of this nature, however, and it is sufficient to assume in the schematic circuits that we are dealing with signals consisting of zeros and ones which are perfectly synchronised. It is convenient for this purpose to think of time, not as being continuous, but as coming in a sequence of ticks; corresponding to each tick the signal at each point of a circuit is defined as 0 or 1. With this understanding we proceed to the definition of our schematic symbols. It should be recognised that these symbols do not necessarily possess a unique equivalent in the actual electronic circuitry. A particular symbol may correspond to a number of entirely different electronic circuits; all that is implied is that the logical effect of the true circuit is the same as that in the schematic circuit.

## Direction of propogation.

An arrow on a line indicates the direction in which signals are propagated. Thus in fig.1 the signal is travelling from A to B.

#### Simple delays.

If the arrow is converted into a triangle as in fig.2 there is a delay of one unit in passing from A to B, so that if a is the signal at A at time n, and b that at B, then  $b_n = a_{n-1}$ .

#### Long delays.

A delay of a number of units is shown as an elongated rectangle with the delay within it. In fig. 3, for example, there is a delay of four units in passing from A to B.

### Change of polanity (negation).

A short stroke across a transmission path indicates a change of polanity i.e. zeros and ones are interchanged. Hence in fig.4  $b_n = 1 - a_n$ .

Junction of transmission paths.

A transmission path may be allowed to bifurcate, in which case the signal is transmitted simultaneously on both forks. E.g. in Fig.5 a = b = c .

Transmission/

Transmission paths are sometimes shown converging as in Fig. 6. This is not normally done unless the circuit is such that it is not possible for a one to appear simultaneously on more than one of the tributary converging lines. The signal in the main stream is then defined to be a one if the signal in any tributary is a one, and to be a zero if the signals in all tributaries are zero. Limiters.

A limiter is shown as a circle containing a number m, known as the threshhold of the limiter, with any number of inputs and outputs (Fig.7). The limiter gives an output of one on all output lines if the input is 'm' or more ones, and an output of zero otherwise. In a limiter of threshhold 1 the 1 is omitted. Inhibitive connections.

A limiter may have a second type of input known as an inhibition, e.g. the input B in Fig. 8. The output of the limiter is to be a zero if the input from B is a one, regardless of the other inputs. An input of zero from B is disregarded.

## Triggers.

A trigger is unlike a limiter in that its output at any time depends on its previous history as well as its current inputs. A trigger of threshhold 'm' is shown as an ellipse with the figure 'm' within it. (Fig.9). It has any number of inputs and outputs and at least one inhibition. The trigger is "tripped" when it receives m or more simultaneous ones, and from then onwards its output is a one until such time as it receives a one on an inhibitive connection. It is then "reset" i.e. returns to a condition in which its output is zero. The trigger is said to be 'on' when it is emitting ones, and 'off' when it is emitting zeros. A trigger may have another type of input known as a 'changeover'. Such an input is shown as X in Fig.9A. If the trigger receives a one on a 'changeover' input its state is changed i.e. if it was emitting ones it begins to emit zeros and vice-versa.

## Differentiators.

A circle containing an E (Fig. 10) denotes an element which emits a one after the termination/

termination of a sequence of ones on its input. Thus in Fig.10  $d_n = Max(0, a_{n-1} - a_n)$ . Fig. 12 shows an equivalent circuit. A circle containing a B (Fig.11) denotes an element which emits a one at the beginning of a sequence of ones at its input. Fig.13 shows an equivalent circuit. These elements will normally be realised with "differentiator" circuits. The 'E' and 'B' are intended to suggest the ideas of "end" and "beginning".

#### Manual Controls.

A manual press button is shown as a circle containing an 'M' with an output, Fig. 14. It is to be understood that such an element emits a sequence of ones starting at some unpredictable time, shortly after the pressing of the button. This is actually a slightly troublesome condition to attain, but for the purposes of the schematic diagrams it is sufficient to assume that it has been reached.

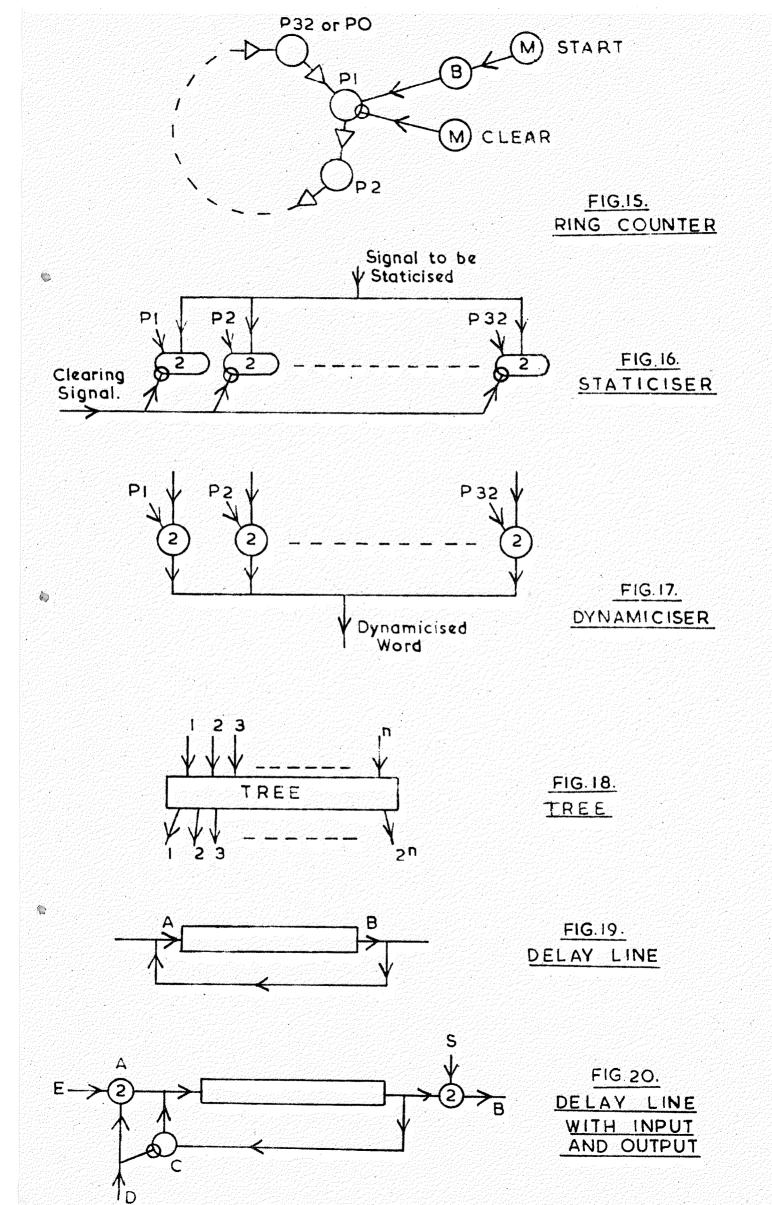

#### Major and minor cycles.

The individual unit of information is, of course, the digit, which may take the values 0 and 1, but it is convenient to consider also units consisting of aggregates of digits. In the pilot model of the A.C.E. a group of 32 digits has been taken as one of our fundamental units of information. An aggregate of 32 binary digits is capable of representing numbers of rather less than ten decimal digits  $(2^{32} = 4.295 \times 10^9)$ . This suggests that we should measure time in groups of 32 'ticks'. These groups are known as 'minor cycles'. It may be helpful to think of the minor cycles as being equivalent to minutes, with ticks at each second. The information contained in the signal appearing at any point during a minor cycle is called a 'word'. Each word then, consists of 32 digits.

This division of time into minor cycles is provided by a circuit known as a ring counter. It is, effectively an electronic commutator and its schematic circuit is shown in Fig. 15. It consists of a group of 32 elements in a ring, each of which is separated from the two adjacent elements by a unit delay; the 32 elements are known as P1, P2, -- P32. At the beginning of operations the CLEAR push button is operated; this removes any stray pulses in the ring counter/

counter; the START push button is then operated and this puts a single pulse into P1. At any subsequent tick one and only one of the Pn's will be emitting a pulse.

The elements of the ring counter are frequently used in the control circuits to supply ones at definite points in a minor cycle. The element PM e.g. supplies a one at the beginning of each minor cycle and thereafter 31 zeros. The pulses supplied by the element Pn are usually referred to as "Pn pulses", and the notation, Pn, is also used to denote the sequence of digits supplied by the element Pn in any minor cycle. This use of "Pn" may appear to be schewhat ambiguous, but in practice the meaning is always abundantly clear from the context.

A period of 1024 ticks or 32 minor cycles is known as a major cycle. There is no need to have anything corresponding to the ring counter for telling the time within major cycles. This is achieved, effectively, by the positioning of the coded instructions, as will appear later. Staticisers and Dynamicisers.

In a number of positions in the circuits it is necessary to convert information from the dynamic form, as a temporal sequence of digits or pulses, into a static form consisting of D.C. voltages on a number of lines, corresponding to the number of pulses. In Fig.16 the circuit used for "staticising" a word of 32 digits is given. It consists of a group of 32 triggers of threshold two, each of which receives the signal to be staticised and one of the Pn pulses. The nth digit of the signal to be staticised trips the nth trigger if it is a one, and fails to trip it if it is a zero. There is also a lead for resetting all the trigger circuits; this must be pulsed before a second word can be "set up" on the staticiser.

Conversely, we may wish to convert a number of static signals into the dynamic form. The static signals may come from triggers or be obtained from a set of switches. The circuit for performing this operation is shown in FIG. 17. It consists of a set of 32 limiters of threshold two, each of which

is supplied with a Pn and one of the static signals. The outputs from the limiters are combined together to produce the static signal, in dynamic form, once per minor cycle.

#### Trees.

If we consider a set of n triggers then there are 2<sup>n</sup> possible states in which they can be, since each one may be either "on" (emitting ones) or "off" (emitting zeros). It is frequently necessary in our schematic circuits to use a set of n triggers to provide an unbroken stream of ones on one of 2<sup>n</sup> different lines. There are a number of different electronic circuits for performing this selection, of which perhaps the most common is a resistance network. Any circuit which performs this operation is referred to, in this report, as a "tree of order n", see Fig.18.

Whenever we have n different sources of D.C. voltage each of which may take one of two different voltages we may use these n sources to select one of 2<sup>n</sup> different lines, i.e. as the basis of a tree of order n. Triggers are the most common examples of such sources of D.C. voltages.

#### Delay lines.

The account given in this report is based on the assumption that the storage medium for the numbers and coded instructions will be accoustic delay lines, though little modification would be needed for any other truly serial method of storage. An accoustic delay line consists essentially of a straight cylindrical tube filled with mercury and with a piezo-electric crystal at each end. It is shown schematically in Fig.19. If a pulse is fed into the delay line at A, the crystal at A sends out a sonic wave into the mercury which travels down the delay line at the velocity of sound in mercury; at point B this disturbance is reconverted into a pulse by the second crystal. If this pulse is now amplified and reshaped it may be fed back into A and in this way the pulse may be preserved indefinitely. Two standard lengths of delay lines are used in the A.C.E. The first type, usually called a long tank is of such a length that a sound wave takes 1024 (i.e. one major cycle) to travel down the

tube. Since our pulses are a microsecond apart, a long tank may be used to store 1024 digits or 32 words. The configuration of pulses in a long tank recurs once per major cycle. The other type of delay line, usually called a short tank or temporary storage (T.S.), is capable of storing 32 digits only i.e. exactly one word. The configuration in a short tank recurs once per minor cycle. In addition to the circuitry needed for the recirculation, each tank is equipped with an input and an output device. This is shown in Fig. 20. If an unbroken stream of ones is supplied along the line marked S, a copy of the contents of the tank is obtained at B, the circulation of the content of the tank being undisturbed. If, on the other hand, an unbroken stream of ones is supplied along the line marked D and a new sequence of digits is fed in at E, this new sequence passes into the tank, whilst the former contents are obliterated at C.

## 3. Arithmetical and logical operations.

## Conventions used in the representation of numbers.

It has already been stated that numbers are stored in the binary system. As far as the units which perform the arithmetic operations are concerned these numbers are treated as though they were integers. The true position of the binary point will vary from problem to problem to suit convenience and its correct manipulation in any given problem will be taken care of by the programming. It is possible that some problems will arise which will necessitate the use of a floating binary point. This means that each number will be represented by an ordered pair of numbers m and n, the first of which is an integer (positive or negative) and the second satisfies  $-1 \le n < 1$ . The number corresponding to the ordered pair (n,n) is  $2^m n$ . In such problems the basic arithmetic operations will also be programmed; in general it may be said that a floating binary point will only be resorted to, when it proves impossible to estimate the necessary scale factors without undue effort. In most problems its use may be eliminated by adjusting the binary point from time to time during the computation, as this becomes necessary.

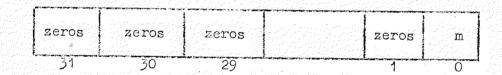

If for the moment we agree to consider our numbers as integers and make one word available for each number, then we can represent all integers 'n' such

that  $-2^{31} \le n \le 2^{31}$  by the following convention. The integer 'n' is to be represented, modulo  $2^{32}$ , by a number, n', such that  $2^{32} > n' > 0$ . In this convention all negative numbers have a 1 in the extreme left hand position and all non-negative numbers, a 0. For this reason  $-2^{31}$  is included and  $+2^{31}$  is excluded. Each number, then, may be said to consist of 31 digits and a sign digit.

If we allow our numbers to be two words in length, then we may represent all integers n such that  $-2^{63}$  n  $2^{63}$ . A number is now represented by 63 digits and a sign digit. Similarly, if we allow m words for our numbers, each number is represented by 32 m-1 digits and one sign digit in the extreme left hand position. A small number, regarded as a number represented in the m word convention, will begin with a long string of zeros if positive, and a long string of ones if negative.

## Arithmetic units.

The Arithmetic units of the A.C.E. are more closely integrated with the logical control than is the case in most other electronic computing machines which have been designed, but it is convenient to consider the basic circuits for performing these operations as separate units at this stage.

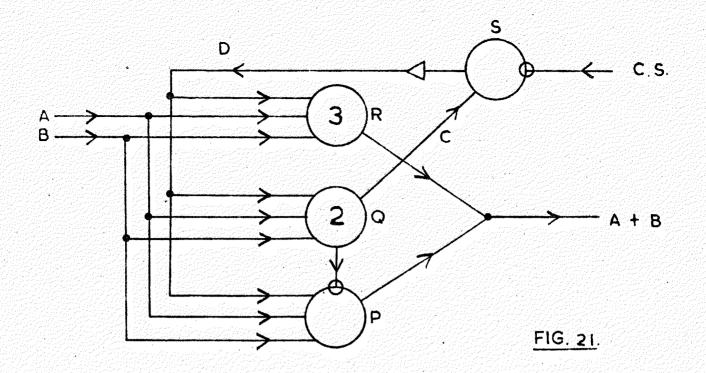

## Addition.

The schematic circuit for addition is shown in Fig.21. To understand how it performs addition let us suppose two sequences of digits  $a_n$ ,  $b_n$  corresponding to numbers A and B are fed in to the adder on the lines on the left hand side. These two sequences must of course be in phase, i.e. the digits in the least significant position must arrive simultaneously. For each digit of the sum (A+B) except the first, we have to consider the problem of adding the two current digits of A and B and the carry over from the previous digit, and forming from them the current digit of (A+B) and the carry over to the next digit. The current digit of (A+B) is fed out on the line marked (A+B) and the carry digit is borne by the line marked (A+B) and unit before it arrives at D. At any stage of the addition, then, the current

digits of A and B and the carry over from the previous stage are each fed to all three of the elements P, Q and R. It is now sufficient to consider four simple cases.

- (i). P, Q and R are each fed with three zeros, In this case a zero is emitted for the current digit of (A + B) and for the carry digit.

- (ii). P, Q and R are fed with two zeros and a one. In this case Q and R are fed with two zeros and a one. In this case Q and R emit zeros and P emits a 1 on the (A + B) line. The carry digit is therefore zero and the current cligit of (A + B) is a 'one'.

- (iii). P, Q and R are fed with one zero and two ones. In this case R emits a zero but P and Q both have sufficient inputs to emit a one. The one emitted by Q however inhibits P and the net effect is that a zero goes out from P to give a zero for the current digit of the sum; and a one goes out on the carry line from Q.

- (iv). P, Q and R are fed with three ones. In this case the threshhold of all three elements is reached. Again P is inhibited by the output of Q and therefore puts cut a zero but R emits a one as the current digit of the sum, and Q gives a carry digit of one on the line C.

It will be seen that each of the above cases gives the result required by the rules of binary addition. The first digit does not require any special consideration. Clearly there is no carry from the "previous stage" and hence there is a zero on the line marked D.

So far we have tacitly assumed that our numbers are indefinitely long and have omitted all reference to the element marked S with the inhibiting connection marked C.S. Suppose now we restrict our numbers to be one word in length. If we are to use our convention for numbers with a sign, then, even in the simplest case of the addition of two positive numbers, we cannot expect the adder to give the correct answer unless it lies in the permitted range. E.g. consider the addition/

addition of  $2^{30} + 1$  to  $2^{30}$  shown below. The answer given by the adder interpreted by the

0100 ...... 001 + 0000

same convention is negative since it has a 1 in the extreme left hand position; it is in fact  $-2^{31} + 1$  according to this convention. Hence if we are to use the convention all the time the answer to this addition is only given correctly, modulo  $2^{32}$ . Provided the true sum is such as to lie in the permitted range, however, it will be exact. Consider now the addition of 6 and -5. The number 6 will be represented by 6 but the number -5 will be represented by  $2^{32} - 5$ . The addition as performed by the adder is shown below.

0000 ..... 00110 representing 6

1111 ..... 11011 representing -5

1 0000 ..... 00001

The adder will produce first a 1 and then 31 zeros but it will also produce a carry one from the thirty second digit. This carry over at the thirty second digit is suppressed by feeding a P32 on the lead marked C.S. (carry suppression) at the end of each minor cycle. By this means the adder can perform correctly the addition of any two numbers, either positive or negative, which lie in the range permitted by the convention, provided the true sum also lies in this range. Otherwise the sum given by the adder, interpreted in our convention, will only be correct modulo  $2^{32}$ . If we consider the addition of double length numbers a similar problem arises, but now we must suppress the carry over at the P32 position corresponding to the sign of the number and must not suppress it at the P32 position occurring in the middle of the number. This is achieved by means of a source which gives a P32 at the end of alternate minor cycles. Full

consideration/

consideration of this point and the addition of multiple length numbers is given later.

## Subtraction.

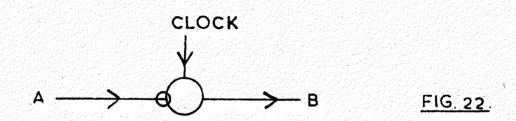

The operation A-B is performed effectively as  $A + (2^{32} - B - 1) + 1$ . The number  $2^{32} - B - 1$  may be obtained from B by interchanging zeros and ones i.e. by a polarity change. If we assume we have a standard clock which is emitting an unbroken stream of ones, then this polarity change may be achieved by the circuit in Fig. 22 which operates as follows. If the digit in line A is a one, then the clock is prevented from passing a one to B and hence we obtain a zero at B; if the digit in line A is a zero then line B receives a one from the clock. A-B, then, is formed by sending A and  $2^{32} - B - 1$  to the adder and feeding a P1 pulse in the carry line to account for the extra 1. As in the formation of A + B, we obtain the correct answer to A-B, within the convention, provided the true answer is in the permitted range. A and B may be either positive or negative. For double length numbers, the P1 has to be added in the first P1 position of the number but obviously not in the second P1 position. This is a similar problem to that of the suppression of the carry digit in double length addition.

#### Multiplication.

It is convenient, for the sake of simplicity, to ignore our sign convention for the time being and to consider the multiplication of two positive numbers A and B each of which satisfies the inequalities

We define a and b to be the n<sup>th</sup> binary digits of A and B, a and b being the least significant and there being 32 binary digits in each number. If either of the numbers is small there will be a number of zeros in the more significant places of that number. The product X, of the two numbers, may be regarded as a 64 digit number of which any number of the more significant digits may be zeros. If the number A be regarded as the multiplier and B as the multiplicand/

## WORKING OF MULTIPLIER

Showing content of Tanks I and 2 at end of minor cycle m+x, for x=0,---,66.

| <u>×</u> <u>Tank i</u> | TANK 2                                             |

|------------------------|----------------------------------------------------|

| O 32 A I               |                                                    |

|                        |                                                    |

| 2 31 A I 32            |                                                    |

| 3 32 A 100             | 32 X <sub>1</sub> I                                |

| 4 30 A 1 32 31         | (first addition begins)  32 X <sub>I</sub> I O     |

| 5 32 A 1000            | (first addition not quite ended)  32 X2   32 X1 X1 |

| 6 29 A I 32 31 30      | 34 X2 1 0  (extra due to possible carry over)      |

| 64 32 A 1              | (last addition begins) 063 X31 10                  |

| 65[32 A I]             | 32 X32 I O 63 X31 32                               |

| 66 32 A 1 O            | (last addition ends)  64 X32 I O                   |

multiplicand then the product may be formed in the following steps

$$X_1 = a_{32}B$$

(1)

$X_2 = 2X_1 + a_{31}B$  (2)

$X_3 = 2X_2 + a_{30}B$  (3)

$-----$

$X_n = 2X_{n-1} + a_{33-n}B$  (n).

$-----$

$X = X_{32} = 2X_{31} + a_{1}B$  (32).

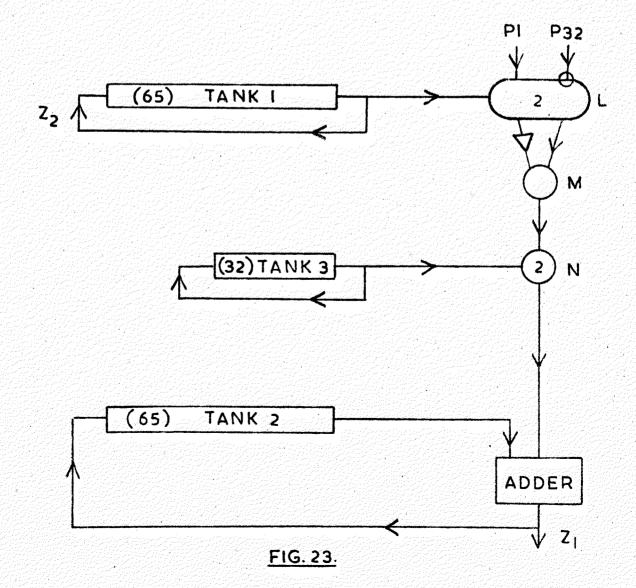

The number  $X_i$  may be called the i<sup>th</sup> partial product. To form  $X_{i+1}$  from  $X_{i}$ , A and B, we multiply  $X_{i}$  by 2 and add to it B or zero according as a is one or zero. The circuit for performing this operation is shown in Fig. 23. It consists of two tanks of length 65 units and one ordinary short tank. Let us suppose that initially the two 65 digit tanks are empty and the 32 digit tank contains B, and that in minor cycle number 'm' the multiplier A is sent to tank 1 (i.e. the upper 65 digit tank). Nothing will happen until the trigger L is tripped and this can only occur if tank 1 emits a one at time P1. Throughout the multiplication, tank 1 will contain the multiplier and 33 zeros. The first opportunity L has to be tripped is at the P1 time of minor cycle (m+3). Which we denote by (m+3)1,; at this time the a32 digit is received by L and it will therefore be set up or not according as a 1 or 0. When L is set up, M emits 32 consecutive ones and this enables the contents of tank 3 (i.e. B) to pass through N. During minor cycle (m+3) then, a B passes into the adder and is added to the contents of tank 2 (i.e. zero). to form  $X_1$ . In (m+4), one of the 33 zeros is omitted from tank 1 and therefore L is not tripped. Since tank 1 is of length 65 its contents are delayed one unit for each circulation and therefore in (m + 5), tank 1 emits a ... Hence the adder receives a ... B from M. The content of tank 2 will also be delayed one unit and will therefore be transmitting 2X, to the adder. Tank 2 therefore receives  $(2X_1 + a_{\overline{3}1} B)$ i.e.  $X_2$  during minor cycle (m + 5) and the 1st tick of (m + 6) if  $X_2$  should be

as long as 33 digits. Similarly in  $(m + 6)_1$  the trigger L receives one of the 33 zeros and in  $(m + 7)_1$  it receives a ... Hence in (m + 7) and (m + 8)tank 2 receives  $X_{\chi}$ . The process proceeds with L receiving the successive digits of A and one of the 33 zeros in alternate minor cycles, and tank 2 receiving the successive partial products. It is evident that tank 2 receives  $X_{i}$  from the adder during minor cycles (m + 2i + 1) and (m + 2i +2) and therefore the product X or  $X_{32}$  is available at  $Z_1$  in minor cycles (m + 65) and (m + 66). The multiplier has been described with two tanks of length 65 for clarity; the second tank of length 65 can easily be dispensed with in the following manner. The partial product X, cannot contain more than 32 + i digits, and at the stage at which it is formed we have already made full use of i digits of the multiplier. If the successive digits of the multiplier are obliterated immediately after use, then the partial products may be stored in the same tank as the remaining part of the multiplier and there will, in fact, always remain one zero at least between the partial product and this remainder of the multiplier. Hence tank 2 is removed, the output of tank 1 is fed into the adder and the output of the adder back to the input of tank 1. Tank 1 now has no recirculation except via the adder. The only other alteration (in addition to the simple device for removing the successive digits of the multiplier as they are used) is that the trigger L, must now be supplied with alternate P1's only. This is because in the simplified diagram we made are of the fact that tank 1 contained the multiplier and 33 zeros, and one of these zeros reached L at alternate P1 times. The space occupied by those zeros is now replaced by the partial products and these must not be allowed to trip L.

So far we have considered the multiplication of positive numbers only and have ignored our sign convention. Suppose we use the multiplier as it stands to form the product of plus six and minus five. These numbers will be represented by 6 and  $2^{32} - 5$  and hence it will produce the answer  $6(2^{32} - 5)$ . To produce the correct answer regarded as a signed number of two word length we must add  $2^{32}$  ( $2^{32} - 6$ ) using a two word adder; this gives  $2^{64} - 30$  which is

the correct answer within the convention. For the multiplication of minus six by minus five, the multiplier produces  $(2^{32}-6)$   $(2^{32}-5)$ . If we add to this result  $2^{32} \times 6$  and  $2^{32} \times 5$  using a two word adder then we will obtain the true answer, 30, since the extra  $2^{64}$  will be the carry which is suppressed. It is easy to see from these examples that, in order to obtain the true answer for the product of two signed numbers in the standard convention for two-word signed numbers, the value given by the multiplier must be corrected according to the following rule. If either of the factors is negative then we must add  $2^{32} \times (2^{32} - 0)$  other factor) using a two-word adder.

The basic circuit for multiplication may be extended in a number of ways. Its speed may be doubled, for example, simply by multiplying by two digits of the multiplier for each circulation. This would require the following alterations. The tank of length 65 units must be extended to 66 units, the elements L, M and N must be duplicated and the second trigger corresponding to L supplied with a P2 instead of a P1, and two adders must be used instead of one. Similarly, by using four adders, the speed may be quadrupled and so on. Since adders are quite simple in a serial machine this does not involve very much extra apparatus: The multiplier may also be extended to put in the corrections required for 'signed' multiplication automatically. Finally it could be made to produce a 32 digit answer correctly rounded off, if this should prove advantageous. The form of multiplier we intend to use will be discussed later.

## Division.

An automatic dividing unit may be constructed, either using the same tanks as are used for multiplication, in which case one digit of the quotient is obtained every two minor cycles, or using short tanks only, in which case one digit per minor cycle can be obtained: In this report, however, we shall assume that the A.C.E. has no automatic divider; division will always be programmed, using a standard table of instructions.

## The logical operations.

In addition to the fundamental arithmetic operations we used a number of logical/

logical operations; the circuit for performing these operations may be expressed very simply by means of our standard symbols. The logical operations are defined below.

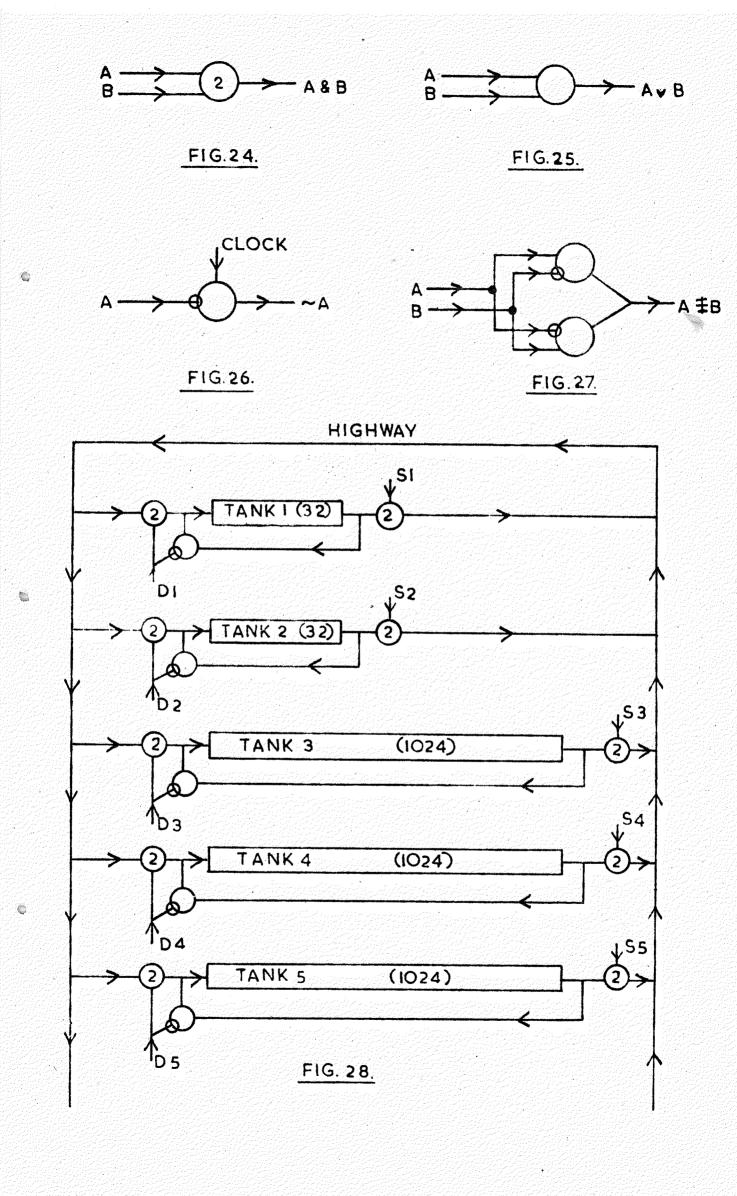

- (i) A & B = C. The operation A 'and' B on two sequences of digits, A, B, produces a sequence of digits, C, such that  $c_n$  is a one if both  $a_n$  and  $b_n$  are ones, and is a zero otherwise. (Fig. 24).

- (ii) AvB = C. The operation A 'or' B produces a sequence of digits, C, such that  $c_n$  is a 'one' if  $a_n$  or  $b_n$  is a 'one' or if both are ones, and  $c_n$  is a zero only if  $a_n$  and  $b_n$  are both zeros (Fig. 25).

- (iii)  $_{n}$  A = C. The operation, 'not' A, produces a sequence of digits C such that  $c_n = 1-a_n$  i.e. zeros and ones are interchanged (Fig. 26).

- (iv) A  $\not\equiv$  B = C. The operation A 'not equivalent to' B, produces a sequence of digits C such that  $c_n = 1$  if  $a_n \not\equiv b_n$ ,  $c_n = 0$  if  $a_n = b_n$  (Fig. 27).

## 4. Logical Control of the Pilot Model.

## General considerations on the coding of instructions on the A.C.E.

Although the logical control of the full scale A.C.E. is much more comprehensive than that of the pilot model, it may be regarded as a natural extension of the latter. For this reason we describe the logical control of the pilot model in detail and then sketch the extensions made in the full scale A.C.E.

A fundamental feature of the control of the pilot model is that every coded instruction is regarded as a transfer of a sequence of digits from one of a number of positions in the machine known as 'sources', to one of a number of positions known as 'destinations'. We shall consider, first of all then, the problem of transferring numbers from one tank to another.

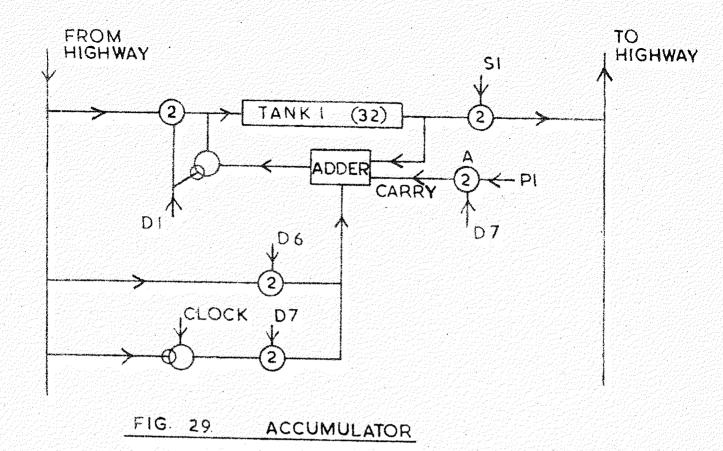

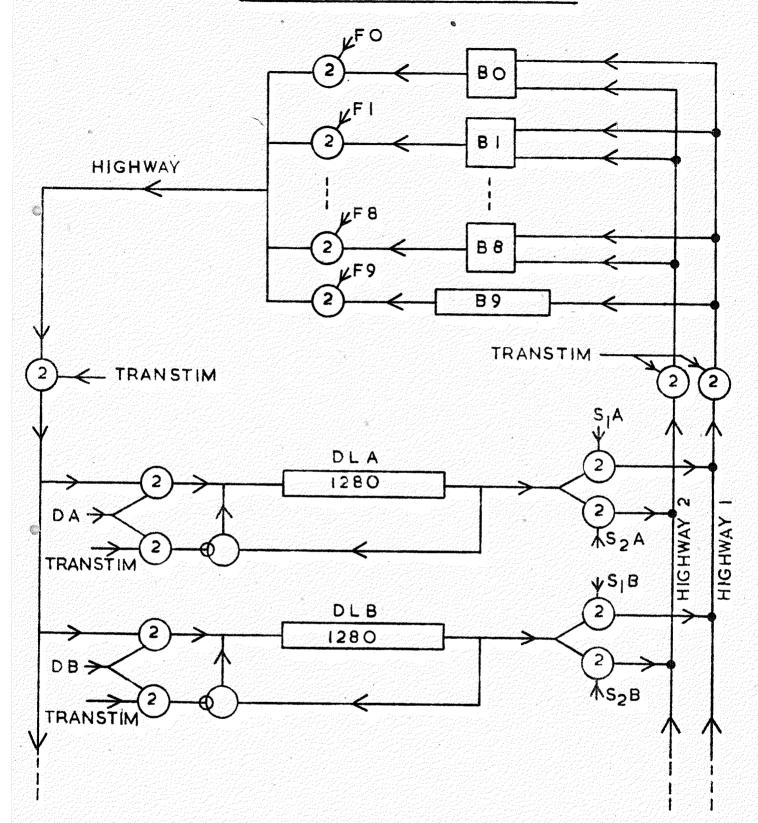

Suppose we have a number of short tanks and long tanks, each with an input and output device of the type described in Section 2 and each of the outputs of the tanks is connected via a common line called 'highway' to each of the inputs. Such a system consisting of two short tanks and three long tanks is shown in Fig. 28. Each of the tanks is assigned a number. Suppose we wish to transfer a number from tank no.1 to tank no.2 both being short tanks. We have only to supply/

supply an unbroken stream of ones on the lines marked S1 and D2 for a period of time not less than 32 microsecs.; a copy of the contents of tank no.1 will then pass out into highway and the ones on the line D2 will enable them to pass into tank 2. After the operation has been carried out for 32 microsecs. its continuation serves no further purpose. As long as we confine ourselves to short tanks, any transfer may be described by an order consisting of two numbers e.g. the operation of transferring the contents of tank 1 to tank 2 may be written, 1-32. If we consider the problem of transferring a number of words from one long tank to another long tank then, in addition to specifying the two tanks involved, two further numbers are required which specify, in some manner when the transfer begins and when it ends. Unless the transfer begins and ends at the correct time the required words will not be transferred. Two remarks are pertinent at this stage; first it has been assumed that the words in two tanks are in phase; this requires the use of the ring counter; secondly the transfer from one long tank to another can only replace words of the receiving tank by the corresponding words of the source tank. The instruction needed has now become of the form  $S \rightarrow D$ ,  $T_1$ ,  $T_2$ . Where  $T_1$ ,  $T_2$  are numbers required to time the transfer correctly.

So far the instruction has been used to effect a pure transfer, but it can be made to perform arithmetic and logical operations in quite a simple matter. Suppose we place an adding unit in the circulation of a short tank, as shown in Fig. 29, and, as a second input, we have a line connected to highway via a destination 'gate'. We may give this destination gate a number, just as we assigned a destination number to each of the tanks. The result of transferring a number from any of the sources to this new destination is to add that number to the number already contained in the tank with the adding unit: this tank has now become an "accumulator". Since the adder is associated with a tank of length 32 the adder will need carry suppression at the end of every minor cycle. As an example of the type of operation which a single

transfer,

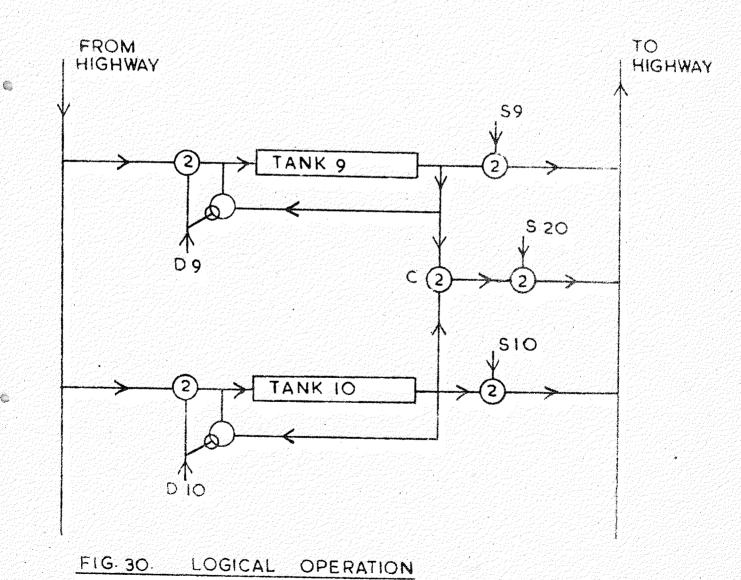

transfer can perform, we consider the transfer of m consecutive words of a long tank to the accumulator; the accumulator will form the algebraic sum of the m numbers plus its original contents. The tank plus adder will now have effectively two inputs. An input through the adder for adding numbers to its original contents, and a normal input for replacing its original contents by the number received. The accumulator may be used for subtraction by providing it with another destination which receives the complement of the number travelling in highway and transmits it to the adder. This is shown as destination 7 in Fig. 29. The ones in the line D7 must also be used to insert a P1 in the carry position when subtraction is performed. This may be done as is shown at element A in Fig. 29. Logical operations can be effected by a transfer in a similar manner. Fig. 30. shows how we can form the sequence A & B from two sequences A and B. Suppose the outputs of two short tanks are fed continuously, into a limiter of threshhold two; the output of this limiter will be A & B if A, B are the contents of the two tanks. If this limiter is supplied with a source gate and is assigned a number then A & B may be called upon by a transfer in the same way as any other source. In Fig. 30 the "and" facility has been provided on tank 9 and tank 10 and it has been given source number 20. It will be seen that Tank 9 and Tank 10 is being produced continuously at the output of the limiter C, but is only passed into highway when a sequence of ones is applied on the line marked S20. The operations A v B may be provided in a similar manner. In addition to the natural sources and destinations and the functional types, a number of rather special sources and destinations may be provided. The pattern emitted by the P1 element, for example, which consists of a one in the least significant position followed by 31 zeros is frequently required and may be used as a source, by supplying the P1 element with a source gate and a source number; the P32 pattern is also very useful. Similar sources are the clock, which provides 32 ones, and a blank, which supplies 32 zeros,

With this extension of the sources and destinations it will be seen that any/

any computation can be reduced to a sequence of coded instructions each of which is of the form  $S \rightarrow D$ ,  $T_1$ ,  $T_2$ , where S is any source, D is any destination and  $\mathrm{T}_1$  and  $\mathrm{T}_2$  are two timing numbers. Our coded instruction contains one other element which serves to determine which instruction is to be obeyed next. The most obvious way of arranging the coded instructions in the memory is to let each instruction comprise one word, and place successive instructions consecutively in long tanks. This has the disadvantage that after the control has read one instruction it cannot receive the next instruction until one complete major cycle afterwards. Since most of the manipulation will be performed on numbers which are being stored temporarily in short tanks this involves an unnecessary waste of time. The alternative adopted, is to space the instructions in such positions in the instruction tanks, that when one instruction is completed, the next is in the correct position for being obeyed. This will be explained more fully when the schematic circuits for the logical control are described. Using this method of spacing, it is sufficient for each instruction to give the number of the tank containing the next instruction; its position in that tank need not be specified since the programming is arranged in such a manner that this next instruction is available when the current instruction is completed.

The standard instruction in the pilot model therefore assumes the form, S = D, N,  $T_1$ ,  $T_2$  where N is a number selecting the tank containing the next instruction. Before we can describe the schematic circuit of the logical control which interprets the code we must know the exact position of the elements S, D, N,  $T_1$  and  $T_2$  in the code word. The pilot model has 32 sources and 32 destinations; hence five binary digits are needed to represent each. Of the thirteen tanks used for storage (7 long and 6 short) only eight are used for storing instruction (7 long and 1 short) and hence three digits only, suffice to specify the tank containing the next instruction. Each of the timing numbers  $T_1$  and  $T_2$  is permitted to vary between 0 and 63 and hence 6 binary digits are required for each. The position in the word occupied by each of these

elements/

elements is as follows:-

P3 to P7 Source number.

P8 to P12 Destination number.

P13 to P15 Next instruction\_number.\_\_

P19 to P24 T

P26 to P31 T<sub>2</sub>

All other digits in the instruction words are spares and will be zeros.

Details of the components of the logical control.

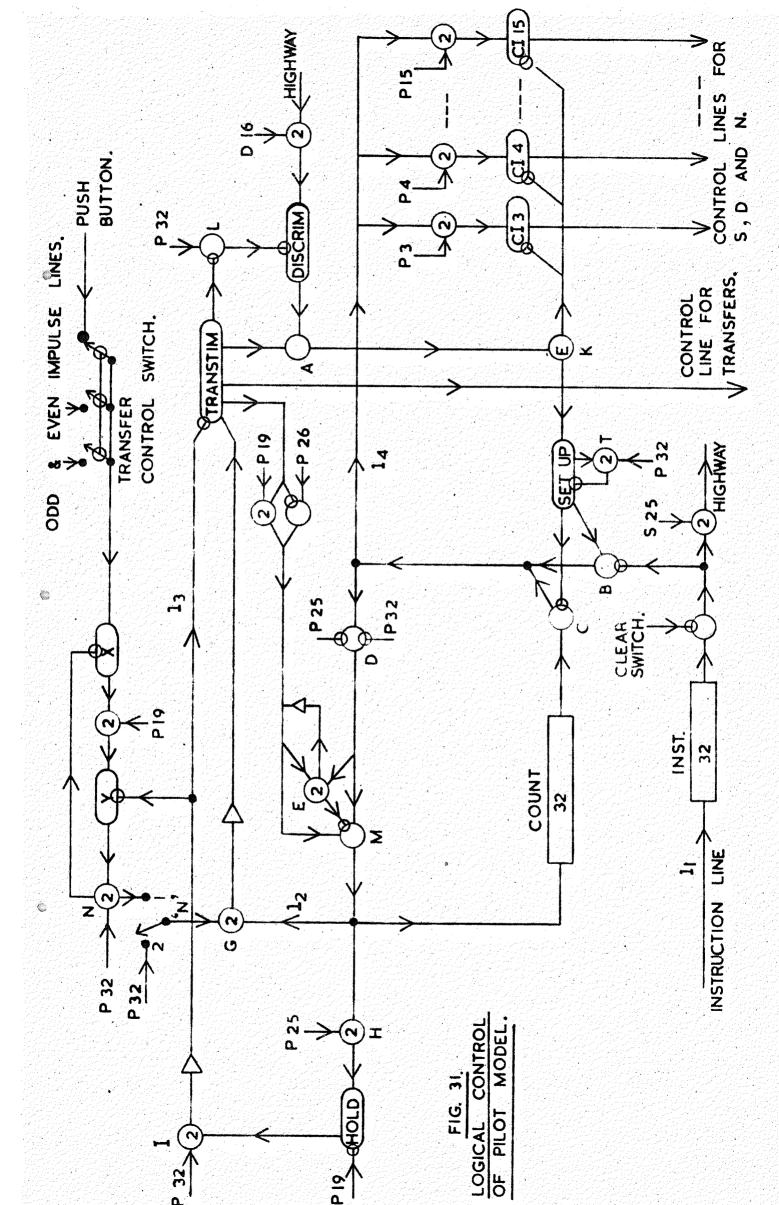

The schematic circuit for the logical control is given in Fig. 31. Before its functioning as a complete unit is described, we will consider the more important components separately.

## (i) Staticisers for source, destination and next instruction source.

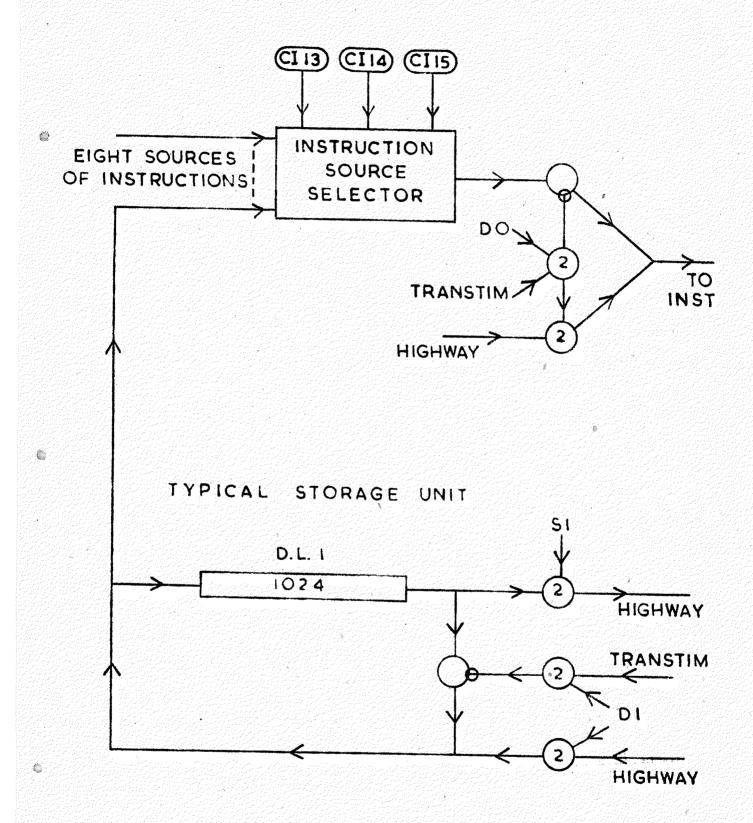

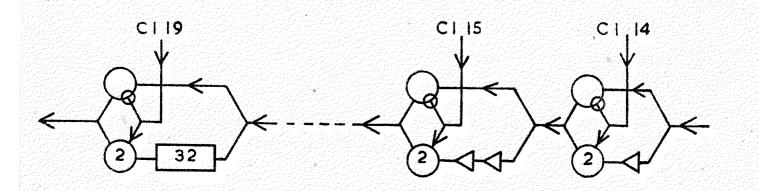

The digits detailing the source, destination and the next instruction source are staticised on the thirteen triggers numbered CI3 to CI15 in the bottom right hand side of the control diagram. (The notation CIn refers to the n<sup>th</sup> digit of the "current instruction"). Triggers CI3 to CI7 control a tree of order five and thereby provide an unbroken sequence of ones of the source gate selected by the instruction. Similarly the triggers CI8 to CI12 select the required destination by means of a tree of order 5 and the triggers CI13 to CI15 select the next source of instruction by a tree of order 3. All these triggers retain their information throughout the transfer and are reset or "cleared" just before the next instruction is staticised.

## (ii) The instruction delay line (length 32) INST.

During the time that a transfer is being performed the instructions from the tank which is to supply the next instruction, feed continuously into the short tank marked INST. The instruction which is trapped in INST when a transfer ceases, becomes the next instruction to be obeyed. The method by which the next source of instruction is selected and directed to INST is shown in Fig.32. Although the number, N, which selects the next source of instruction varies

from/

CONNECTION OF INSTRUCTION SOURCES FOR PILOT MODEL.

from 0 to 7, the numbers of the tanks which hold the next instruction are 1 to 8. This is because source 0 and destination 0 have to be used for rather special purposes connected with the "initial input" problem. For this reason when the next source of instruction number is N, the next instruction comes from tank number 'N + 1'.

## (iii) The trigger TRANSTIM

The trigger, TRANSTIM, is the heart of the control since it determines the actual period during which transfer from the source to the destination takes place; a transfer is taking place if and only if TRANSTIM is on. Up to the present it has always been assumed that provided a source and a destination were being supplied with ones a transfer was taking place. This was convenient before the control circuit was described, but is not, in fact, strictly true. There is a main gate in highway which is operated by TRANSTIM; until TRANSTIM is on, nothing can pass along highway although a source gate and a destination may be receiving ones. Similarly, there are provisions to ensure that a delay line does not have its contents replaced by the number in highway, even though its source gate is supplied with ones, until TRANSTIM is on. These are shown for a typical tank, in Fig. 32.

#### (iv) The counter.

The counter consists essentially of a short tank with an adder in its circulation and also an element D which removes any ones in the P25 or P32 positions. If TRANSTIM is off the number in the tank has a P26 added to it once per circulation until a digit is formed in the P32 position; this P32 digit then putsTRANSTIM on (assuming switch 'N' is at position 2) and is immediately removed at D. When TRANSTIM is on, the number in the tank has a P19 added to it once per circulation until a one is formed in the P25 position. This is detected by the element H, remembered by the trigger "HOLD" until the next P32 time when it puts TRANSTIM off again. It will be seen that the counter acts as a timing mechanism for determining when TRANSTIM is put on

and off. Since the adder is merely called upon to add the single digits P19 or P26 to the number in COUNT, there is no stage at which we have two current digits and a carry over; hence the adder in the circuit may be of the simplified type usually termed 'a half adder'.

## (v) The trigger SETUP.

Operation of logical control.

6

The trigger SETUP is put on for a period of one minor cycle after each transfer. It supplies the next instruction, with ones and zeros interchanged, to the counter and then puts itself off via the gate T.

The description of the operation of the control as a whole may now be given. It will be assumed for the time being that switch 'N' is set at position '2 so that triggers X and Y may be ignored; trigger DISCRIM may also be neglected at this stage.

Let us suppose that the previous instruction was completed at the end of minor cycle number m, and that at the time when it was completed the instruction 'trapped' in the delay line INST (bottom of figure) was

$$S \longrightarrow D;$$

$N;$   $T_1,$   $T_2$ .

Since this ran into INST during minor cycle m, it must have occupied the mth position in the instruction tank from which it was derived. On the termination of the transfer TRANSTIM goes out and (since we are ignoring the effect of DISCRIM for the moment) the end element K sends out a one which clears the staticisers and puts SETUP on. SETUP will therefore be on during the whole of minor cycle (m + 1). During this minor cycle (m + 1) SETUP will delete the present contents of COUNT, at the element 'C', and will feed into the COUNT circuit, the new instruction with its polarity changed, via the element B. The result of the polarity change is that the instruction

31 - S, 31 - D, 7 - N, 63 -  $T_1$ , 63 -  $T_2$  passes via D into count. Positions P25 and P32 of the instruction, before polarity change, were blank i.e. zeros and hence they are ones when they go into/

F.

into element D. At D the P25 and P32 are removed. Since TRANSTIM is off, the adder will be adding P26's, and hence at the end of minor cycle (m + 1) the instruction in count will be

31 - S, 31 - D, 7 - N, 63 -

$$\mathbb{T}_1$$

, 64 -  $\mathbb{T}_2$ °

During the same minor cycle, (m + 1), the parts of the instruction relating to S, D and N will be staticised on CI13 to CI15; it will be noted that 31-S, 31-D and 7-N are staticised instead of S, D and N but this is of no significance since this merely determines the particular manner in which the triggers CI13 to CI15 are to be used to perform the selection. By the end of minor cycle (m + 1) the source, destination and next instruction source are statisfied and the number in COUNT has  $63-T_1$  and  $64-T_2$  in the positions occupied by the timing numbers.

In each subsequent minor cycle the number 64-T2 is augmented by one, due to the addition of P26 until finally in minor cycle  $m+1+T_2$  it becomes 64 and thereby provides a one in the P32 position. This passes via line  $1_2$ through the gate G and, after being delayed 1 us, to TRANSTIM, which is put on. The one in the P32 position is obliterated at D on the next circulation. Immediately TRANSTIM is put on the gate on HIGHWAY is open and the transfer begins to take place. The number  $T_2$  therefore determines how long the control 'waits' until it permits the transfer to start. Since TRANSTIM is now on, COUNT will have a P19 added in each subsequent minor cycle; this means that the number which was originally 63-T, will be augmented by one in each minor cycle until in minor cycle  $m + 1 + T_2 + T_1 + 1$  i.e.  $m + T_1 + T_2 + 2$  it will become 64 and will provide a one in the P25 position. This P25 passes through the gate H and puts on the trigger HOLD. The trigger HOLD sends out ones from P25 onwards until the P32 line, when one of these ones is permitted to pass the element I whence it passes via 13 after a unit delay, to TRANSTIM, which it puts off. Hence TRANSTIM goes off at the beginning of minor cycle  $m + T_1 + T_2 + 3$  after having been on for minor cycles m +  $T_2$  + 2, m +  $T_2$  + 3, ..., m +  $T_2$  +  $T_1$  + 2 i.e. for  $T_1 + 1$  minor cycles; this means that the transfer from the source S

to destination D is continued for  $T_1$  + 1 minor cycles (N.B. it is necessary to use  $T_1$  for a transfer of  $T_1$  + 1 minor cycles to span transfers from 1 to 64 minor cycles while using numbers 0 to 63 for the timing number). The numbers  $\mathrm{T}_1$  and  $\mathrm{T}_2$ are known as the 'transfer' and the 'wait' numbers, respectively. For the whole of the time after minor cycle m + 1, the instructions from the instruction source corresponding to the number N have been running into INST. When TRANSTIM is put off in the teginning of minor cycle  $m + T_1 + T_2 + 3$  the instruction which is trapped in INST is the instruction whose position in N is word number  $m + T_1 + T_2 + 2$ ; this is therefore the next instruction to be obeyed and in making up our instruction table, our next instruction must be placed in this position. Two points remain to be clarified (a) the source, destination and next instruction source are staticised digit by digit during minor cycle m + 1, and therefore at various stages during this minor cycle different numbers are set up on the staticiser. This means that before the staticiser reaches its ultimate value, it registers a varying source, destination and source instruction number. It is however of no consequence, because no transfer takes place in this minor cycle and the instruction of mixed origin which passes into INST is never used. (b) The parts 31-S, 31-D, 7-N of the instruction in COUNT pass to the staticiser during every minor cycle of the 'wait' and 'transfer' period; this clearly leaves the staticiser unaltered.

#### Discrimination.

We may now consider the modification produced by the trigger DISCRIM on the operation of the control. The trigger DISCRIM is a device used to effect discrimination. From time to time during a computation it will be necessary to follow one of two courses depending on the result of previous computations. Such a discrimination is achieved in the following way. The trigger DISCRIM is one of the 32 possible destinations, and an instruction is given which either sends an unbroken sequence of zeros to this trigger or a word containing at least one 'one', according to which course the computation should take. If an unbroken sequence of zeros is sent to DISCRIM it will not be put on, but if it receives at least one 'one'

it will be 'tripped'. It will be seen from Fig. 51 that if an instruction is given which puts DISCRIM on, then after TRANSTIM is put off (i.e. the transfer ordered ceases), DISCRIM remains on for one further minor cycle before it is put off via L and provides a sequence of ones to the element A. The effect of this is that the end element K gives out the pulse which clears the staticiser and trips SETUP, one minor cycle later than would normally be the case. Hence if the instruction in position in a long tank is  $S \Rightarrow DISCRIM$ , N,  $T_1$ ,  $T_2$ , the instruction next obeyed will be number  $(m + T_1 + T_2 + 2)$  or  $(m + T_1 + T_2 + 3)$  of tank 'N + 1' according as the instruction tripped DISCRIM or not. Its action on DISCRIM will therefore determine which of two instructions will be obeyed next and thereby affects a discrimination.

## Input and Output.

The Input and Output requirements of the pilot model will be met by using a Hollerith reproducer unit, both for reading in numbers punched in binary form or decimal form and for punching out information in binary or decimal form. Printed decimal information will be obtained by printing from the punched cards. The decision to use Hollerith equipment for the external organs of the A.C.E., in the earlier versions, at least, in spite of the rather low rate of input and output (a Hollerith reader passes 100 cards per minute), was taken for the following reasons. The Hollerith equipment is already completely developed and needs very little modification for use in conjunction with the A.C.E. and it will prove very convenient, particularly in the early stages, to be able to use the standard Hollerith equipment for sorting, collating and other similar purposes. Moreover, there is quite a considerable range of problems which give rise to a large volume of internal high speed computation for quite a small input and output, and for these problems the slow nature of the Hollerith equipment is of little consequence. If, later, the A.C.E. is required to perform computations for which high input and output rates are essential the modifications necessary to change over to another form of external equipment should not prove very extensive.

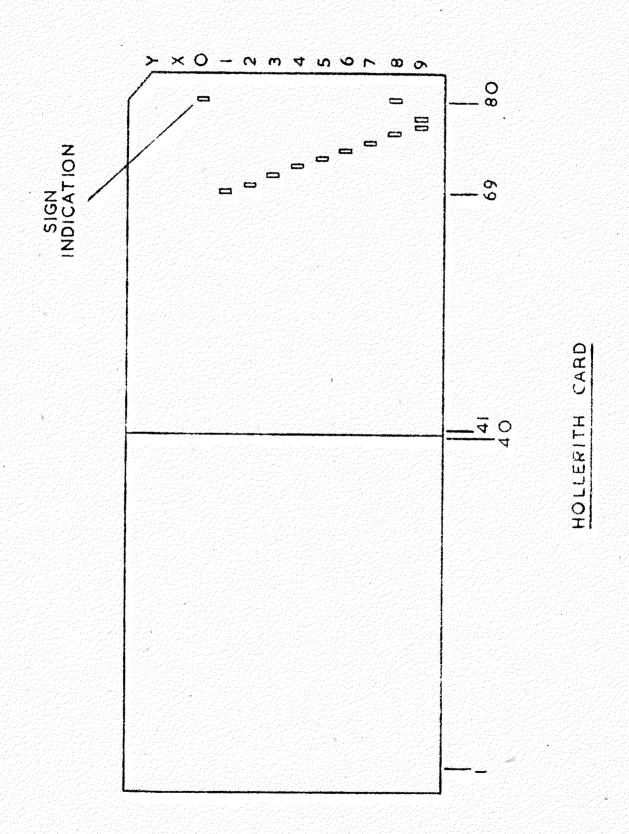

A Standard Hollerith card has 80 columns and twelve rows, the latter being numbered Y,X,0,1,2, .. 9. Of the eighty columns only 32 will be used directly in combination with A.C.E. equipment, namely columns 40 to 71. The other columns will be used for various other purposes, such as recording the identification number of the problem to which it relates and other similar information.

A card bearing binary numbers may have one 32 digit binary number in each of its twelve rows, but only one decimal number will be punched on each card. A decimal number will be punched in standard Hollerith code and since we are not interested in general, in numbers of more than ten decimal digits such numbers will be punched in columns 62 to 71 with a sign indication in the 0 row (zeros may be omitted in punching the number).

The Hollerith equipment is co-ordinated with the A.C.E. during normal operation by the provision of a number of special sources and destinations which are described below.

## Input Dynamiciser.

As each row of a card passes the reading station, the thirty two reading brushes associated with columns 40 to 71 make contact with the Hollerith reader contact roll in each position where a hole has been punched, (Fig. 33). Consequently each of the lines associated with the brushes, is at a positive D.C. voltage (100 volts) or zero, according an there is a hole or not in the corresponding column of the card. These thirty two voltages are dynamicised, and the dynamic sequence obtained is provided with a source gate. For reasons connected with the problem of "initial input" (i.e. the input necessary to get the machine 'under way' when it is started up) the source associated with this input dynamiciser has been made source 0. At any time when a row is being read then, source 0 provides us with the word contained in that row, in dynamic form, once per minor cycle. It will be seen from Fig. 33 that the input dynamiciser may also be connected to a set of 32 manual switches; this means that numbers may be set up by hand and fed into the machine.

HOLLERITH READER CONTACT ROLL -100 VOLT -BRUSHES MANUAL SWITCHES INPUT CONTROL FIG 33 SWITCH. PI P32 INPUT DYNAMICISER. (2  $s \circ \rightarrow$ HIGHWAY HIGHWAY £ ... CLEAR LINE FROM (2 D 29 -> D 30 -> HOLLERITH FIG. 34 (READ (PUNCH) STARTS READER STARTS CARD CYCLE. PUNCH UNIT CARD CYCLE D 27 PRESS. FROM HIGHWAY BUTTON HOLLERITH. PI P 32 <u>FIG. 35.</u> UT STATICIŠER, CONTROLS CONTROLS OUTPUT PUNCH PUNCH RELAY I. RELAY 32.

## READ and PUNCH triggers.

There are two special triggers associated with the input and output functions by means of which the A.C.E. may initiate reading and punching. (Fig. 34). The READ trigger has destination 29 associated with it, and is such that when a signal containing at least one 'one', is sent to destination 29, READ is put on and starts a card cycle (i.e. the passage of one card). The drive clutch holds automatically until the last row of the card is past the reading station. The trigger READ is put off automatically by the Hollerith equipment as som as a card cycle starts. If a further card is required immediately, the drive clutch should remain engaged to avoid loss of time; in order to ensure this, READ must be put on again some time between the reading of the first row and about 60 major cycles after reading the last row. From the point of view of programming the input, all that is essential is that when a second card is to be read, READ must be put on again after reading the first row in order to make certain that this restimulation follows the automatic clearing of READ. The trigger PUNCH, which is associated with destination 30, is connected to the Punch Unit so that when it is put on, a card cycle is initiated in the latter and automatically completed, PUNCH being put off by the Hollerith as soon as the cycle begins.

odd and even impulse line. The rows of the Hollerith are each in the reading position for a number of major cycles (about 6) and between each of the rows there is a somewhat greater number of major cycles; the same is also true of punching. There must therefore be some means of synchronisation between the A.C.E. and the Hollerith which not only makes certain that each row is read (or punched) but also ensures that no row is read twice. This co-ordination is provided by the 'odd and even impulse lines' which are sources 29 and 30 respectively. When any odd row of a card is in position for reading or punching the Hollerith provides a sequence of ones on the odd impulse line; these ones are available at source 29 and thereby we have a method of discriminating whether an odd row is in position or not. Similarly for even

lines, the 'even input line' provides the same facility by means of source 30.

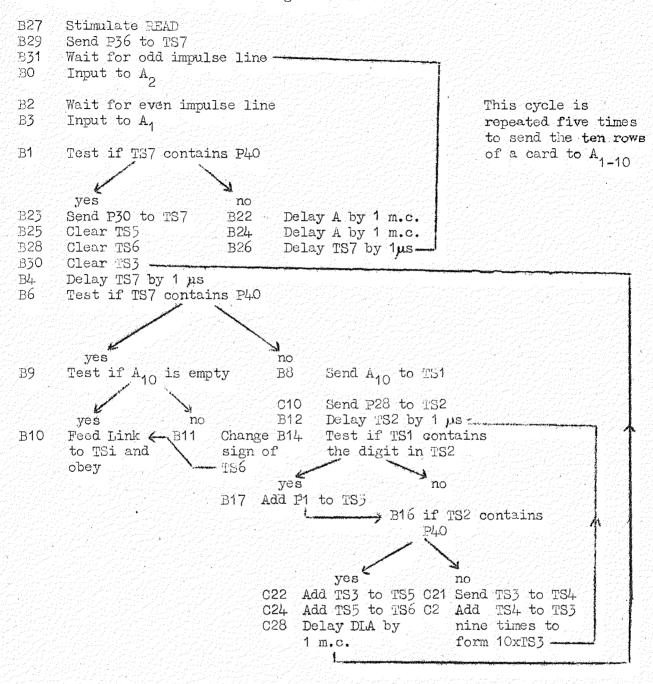

The outline of operations for reading a card is therefore of the form.

- (i) Stimulate READ.

- (ii) Send source 29 (odd impulse line) to DISCRIM the next instruction being to repeat (ii) or go on to (iii) according as DISCRIM receives zeros or ones.

- (iii) Read input i.e. odd row of card.

- (iv) Send source 30 (even impulse line) to DISCRIM, the next instruction being to repeat (iv) or go to (v) according as DISCRIM receives zeros or ones.

- (v) Read input i.e. even row of card.

The above cycle is repeated from (ii) until all the rows of a card are read.

If a further card is required READ is restimulated after the first row has been read.

The outline of the operations for punching a word are similar, viz.

- (i) Stimulate PUNCH.

- (ii) Send source 29 (odd impulse line) to DISCRIM, the next instruction being to repeat (ii) or go to (iii) according as DISCRIM receives zeros or ones.(iii) Set up odd row on staticiser.

- (iv) Send source 30 (even impulse line) to DISCRIM, the next instruction being to repeat (iv) or go to (v) according as DISCRIM receives zeros, or ones.

- (v) Set up even row on staticiser.

etc.

The instructions of type (ii) and (iv) are usually given briefly as "Wait for odd impulse line" and "Wait for even impulse line".

The method by which the rows and cards are counted during input and output will be fully described later.

# External Control of the machine by push button and Hollerith.

For checking purposes it is convenient to have some means by which the control mechanism may be put into "slow motion". The nature of the dynamic storage used in the A.C.E. makes it virtually impossible to do this by

reducing the pulse frequency but it is possible to make the control obey the orders of any instruction table one by one, on the successive stimulation of a push button, in quite a simple manner. It will be remembered that the initiation of transfer in the automatic control is by means of a P32 pulse which has been gated at the element G (Fig. 31). This P32 pulse arises from the slow counter when the counter has raised the number 63 - T2 to 64. If this P32 pulse is not gated at G the number in COUNT in the wait position immediately reverts to zero because the 64 (which is represented by the P32) is deleted at the element D. Failure to gate the P32 pulse at G means that TRANSTIM is not put on, and hence COUNT is still counting in the "wait" position; it will therefore count for another 64 major cycles before it sends out a further P32 pulse to G. As long as G is not supplied with the gating P32 pulses this process of counting up to 64 and then reverting to zero will be carried on indefinitely. If at some subsequent period, gate G is permitted to function, the instruction originally staticised will be executed although it will occur some multiple of 64 major cycles later, than in normal operation. Since the configurations in all the tanks (except those of the multiplier) are repeated every major cycle the delay will not effect the instruction in any way. This is the basis of the push button operation of control, which will now be explained.

Let us suppose that the TRANSFER CONTROL SWITCH has been switched to PUSH BUTTON (Fig. 31 TOP) and the 'N' switch is set at position 1. This means that the gate G is only supplied with ones when the trigger Y is on. Let us suppose further that Y is off and an instruction has been staticised. Until the push button is operated the counter will continue to count up to 64 and then revert to 0 repeatedly. As soon as the push button is operated, a single pulse will be sent to trigger X at some arbitrary time; trigger X will send out ones, and at time P19 one of these will put on trigger Y; from then onwards the gate N will pass P32's to the gate G and also to the inhibitor on X. The first of these will put X off again. The next time the counter sends a P32 pulse to G it will therefore pass through and put TRANSTIM on. The transfer required will then take place, and on its completion TRANSTIM will be put off. The pulse which/

which puts off TRANSTIM will also inhibit Y. Hence the operation of the push button will ensure the performance of one operation only, after which the control will revert to its previous inert state until the push button is operated again. During the inert state the latent transfer will be staticised and therefore the source chosen will be sending out its signal into HIGHWAY, where it will be obstructed because the main HICHWAY gate will be closed. If a scope is fitted on the HIGHWAY before the main gate, the number whose transfer is to be ordered by the instruction may be seen before the instruction is actually carried out. PUSH BUTTON operation therefore provides us with two very useful checking features.

The external control of the machine by means of the Hollerith is achieved in a similar manner. The TRANSFER CONTROL SWITCH is set to 'Hollerith' and as a result of this the trigger X receives a pulse whenever an odd or even row of a card is in the reading position. Thus the control executes one transfer for each row which is read.

## Multiple-purpose components.

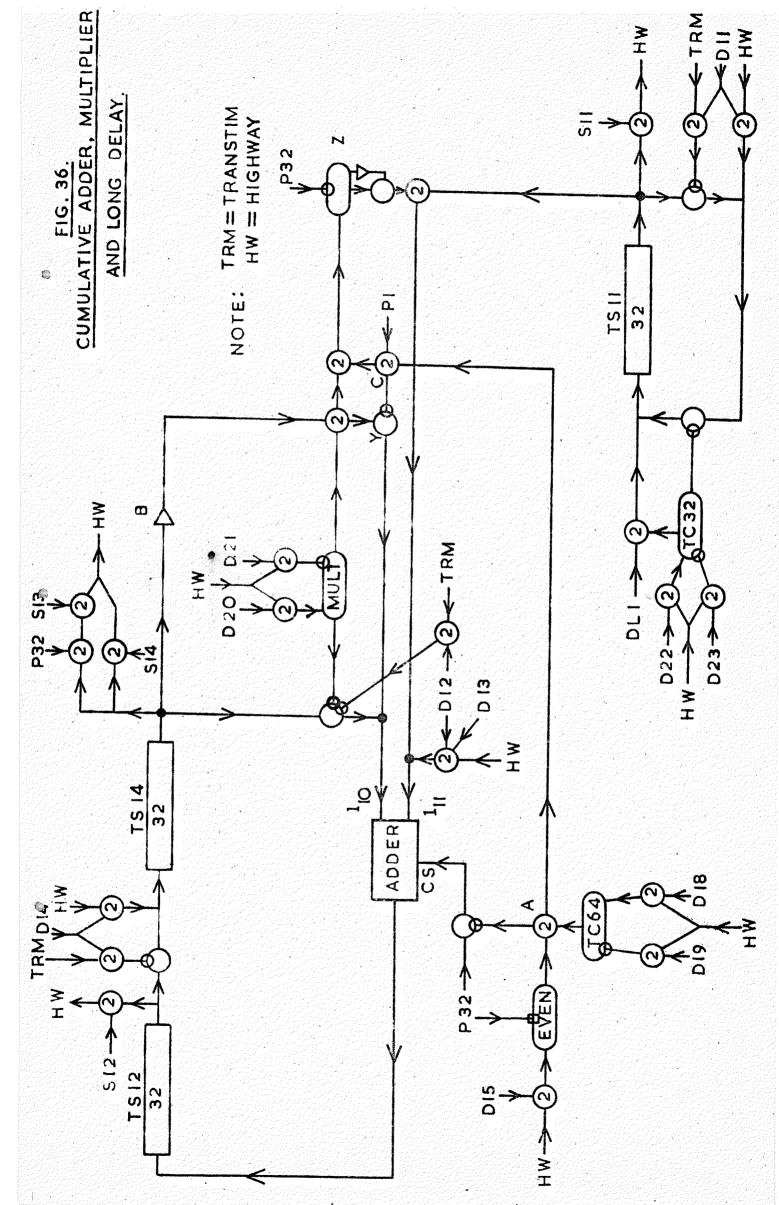

For economy of equipment a number of components of the pilot model are used for dual purposes. One such unit is the short tank, TS11. This tank is normally used as a simple temporary storage, but by setting a trigger its recirculation may be inhibited and its input permanently connected in series with the long tank DL1. The trigger which effects this transformation is shown as TC32 in Fig. 36. The trigger TC32 is set by sending a signal to destination 22 and is reset by sending a signal to destination 23. During a period when TC32 is set, source 11 provides the contents of delay line 1, delayed by a minor cycle. The facility is of very frequent use in repetitive cycles of operations when the words of a long tank are required in succession, one for each cycle of operation. If an order is contained in the cycle which delays the whole contents of a delay line by one minor cycle, then the successive words of that delay line may be transferred by an instruction which always take place in the same minor cycle.

Another multi-purpose piece of equipment is that associated with the accumulator and multiplier (Fig. 36). The accumulator consists of two short tanks TS12 and TS14 in series with an adder. In normal operation each of these short tanks may be used as an accumulator for numbers of one-word length. Numbers may be added to either by sending them to destination 13 at the appropriate time, while each of them has an ordinary destination gate (destinations 12 and 14) by means of which their contents may be replaced by other numbers. When these short tanks are being used as one word accumulators the carry suppression takes place at the end of each minor cycle. The trigger TC64 enables the tanks 12 and 14 to be used as a single two word accumulator with carry suppression at the end of odd minor cycles. This transformation makes use of the trigger marked EVEN which is on in even minor cycles and off in odd minor cycles. If TC64 is put on by a signal to destination 18, triggers TC64 and EVEN together have the effect via gate A of reducing the carry suppression to the end of odd minor cycles only.

A third trigger, MULT, converts the accumulator into a multiplier, for which the multiplicand is stored in TS11. It will be seen that when MULT is put on by a signal to D20, the normal recirculation of TS12 and TS14 is inhibited, and circulation takes place via a unit delay B. The combination TS12, TS14 and the unit delay become effectively the tank of length 65 described in the basic multiplier circuit. Multiplication can only be performed when TC64 is on since it is essential that gate 1 should pass alternate P1's only. (This was explained in the description of the basic multiplier circuit). To perform a multiplication the accumulator must be cleared and the multiplicand sent to TS11. MULT must then be put on and the multiplier sent to the accumulator. When the time taken for multiplication is completed, which will be 65 or 66 minor cycles later according as the 'multiplier' is sent to destination 14 or destination 12, MULT must be put off and the product will be left circulating in TS12 and TS14. An appropriate shift must be given to the product to position the decimal point correctly and the round off may then be applied by adding a P32 to the minor half of the resulting number.

# Miscellaneous facilities in pilot model.

Trigger TC98. The trigger TC98 is used for "remembering" one binary digit. It may be put on by a signal to destination 28 and put off by a signal to destination 24. Typical use of this trigger is for remembering the sign of a number while a number of computations are performed on the absolute value of that number. The trigger may be put on if the number is negative and left off if the number is positive; the state of the trigger may then be used to discriminate between operations which depend on the sign of the number.

INST. The short tank INST which forms an important unit of the control may be used as a source or a destination. It's source number is 25 but its destination number is 0. The explanation of this is given in the section below on initial input. One of its chief uses as a source occurs at positions in an instruction table, where some constant of the computation is required. Such constants are planted among instructions as though they were themselves instructions, and are called upon by using source 25 at the appropriate time. It is also used as a source when, during the course of computation, it is necessary to construct an instruction, some of the elements of which will be determinate when the instruction table is made but other elements of which will depend upon the results of the computation itself. The fixed elements of such an instruction will then be planted among the instructions and the complete instruction built up from these elements at the appropriate time. Numerous examples of this use will occur in the section on coding.

INST is used as a destination occasionally in the course of automatic computation but mainly in the initial input stage of operation. When an instruction is sent to destination 0 it passes into INST, at the same time overriding the next source of instruction which is selected by the current instruction (Fig. 32).

# Temporary storage 9 delayed one unit.

The contents of temporary storage 9 are available, delayed by one unit at source 19. By using an instruction with transfer no. n which transfers source 19 to destination 9 the contents of 9 may be moved round n positions. It should

be noted that by this means a number which consists originally of digits